Sparq-2020系統芯片(SoC)

- 領先其他競爭者, 推出解決方案

- 符合5G 3GPP標準(Rel-15)

- 包括5G PHY和MAC(第1層,第2層)

- 針對URLLC進行了優化 - 包括“Sparq Minislots”和集成移動邊緣計算(“I-MEC”)

- 基於FPGA(16納米技術)

- 通過API啟用自定義

- 主要特點:

- 3 x 200 MHz BW

- 10 Gbps容量(帶載波聚合)

- 延遲<0.5毫秒

- MU-MIMO;光束成形,CoM

Sparq-2020 by RunEL (Video)

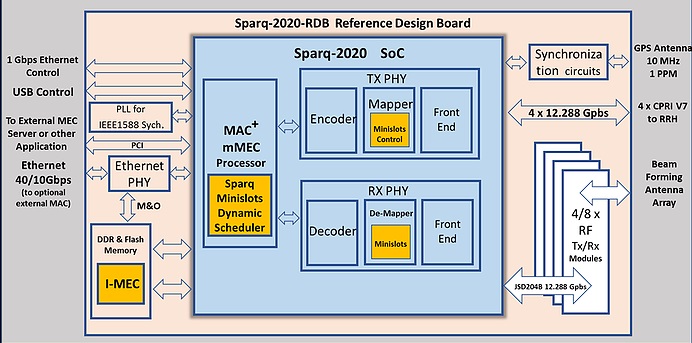

Sparq-2020-RDB(參考設計板)

主要特點

- 提供從設計到商業產品的簡單輕鬆的過程

- 支持5G架構內的不同產品(New Radio,RRH,SRRH等)

- 通過外部RF板接口支持不同的頻率

- 大型FPGA,包括4個ARM內核

- 72bits DDR4 SODIMM 4G連接到ARM內核

- 64bits DDR4到FPGA邏輯

- 嵌入式GPS接收器

- GPS接收器的電池選項,電源關閉時保存RTC

- 編程器時鐘芯片,支持IEEE 1588同步

- FMC連接器

- 4 x 10G SFP +

- 4 x CPRI SFP +(可用於以太網10G)

- 1個USB控制4個UARTS:a-用於CPU,b用於CPU,c-用於FPGA,d-用於GPS

- 2個Micro Connectors : 用於調試

- 5個SMA連接器:a-外部10MHz輸入,b-外部10MHz輸出,c-1pps輸入,d-1pps輸出,e-GPS天線

- 附加時鐘發生器芯片 - 符合超低噪聲JESD204B的時鐘抖動

- PCIe x 4 Gen2用於外部服務器連接或MEC

- 電源輸入:-48V / 24V / 12 V

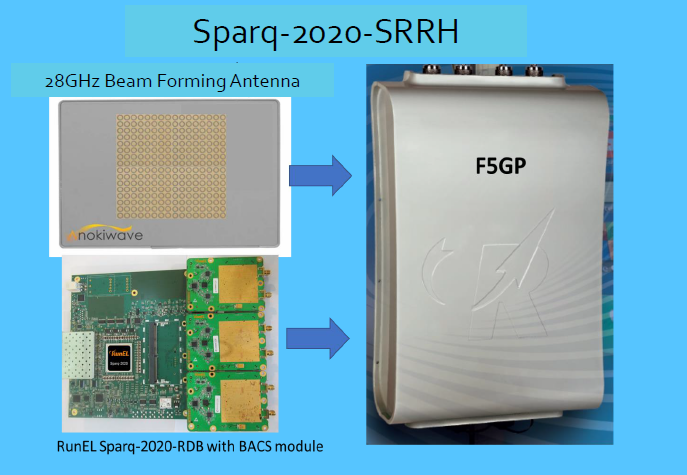

Sparq-2020 SRRH

Sparq-2020 Reference Design Board block diagram